高性能计算和人工智能正在形成推动半导体行业飞速发展的双翼。面对摩尔定律趋近极限的挑战,3DIC Chiplet先进封装异构集成系统越来越成为产业界瞩目的焦点。这种创新的系统不仅在Chiplet的设计、封装、制造、应用等方面带来了许多突破,同时也催生了全新的Chiplet EDA平台,共同为创造下一代数字智能系统赋能。芯和半导体,作为国内首家推出“3DIC Chiplet先进封装设计分析全流程”EDA平台的EDA公司,在10月25日上海举办了2023芯和半导体用户大会,总规模超过600人。大会以“极速智能,

关键字:

芯和半导体 3DIC Chiplet Chiplet

晶圆代工龙头台积电总裁魏哲家24日出席「台积电日本3DIC研究开发中心」开幕启用典礼,日本经济产业相萩生田光一亦出席致词。该中心由台积电设立,并与揖斐电(Ibiden)、新光电气、信越化学等日本逾20家厂商合作,总投资金额达370亿日圆,日本政府透过新能源及产业技术统合开发机构(NEDO)出资190亿日圆。台积电在日本茨城县筑波市产业技术总合研究所设立的台积电日本3DIC研究开发中心24日开幕启用,由于日本已开放台湾人士以商务签证入境且免隔离,魏哲家与台积电先进封装技术暨服务副总经理廖德堆一同出席,说明台

关键字:

台积电 3DIC 材料研发

新思科技宣布其旗舰产品Fusion Compiler RTL至GDSII解决方案自 2019推出以来,已协助用户累积超过500次投片,此项成就扩展了新思科技在数字设计实作领域的地位。使用 Fusion Compiler进行设计投片的客户涵盖领先业界的半导体公司40至3奈米制程节点,横跨高效能运算(high-performance computing; HPC)、人工智能(AI)与第五代行动通讯等高成长的垂直市场。新思科技Fusion Compiler具备统一架构和优化引擎,可促进达成签核准确度(signo

关键字:

新思 Fusion Compiler

要点: 作为新思科技Fusion Platform的一部分,IC Compiler II凭借其行业领先的容量和吞吐量,加速实现了包含超过590亿个晶体管的超大规模Colossus IPU新思科技RTL-to-GDS流程中针对AI硬件设计的创新优化技术提供了同类最佳的性能、功率和区域(PPA)指标集成式黄金签核技术带来可预测且收敛的融合设计,同时实现零裕度流程新思科技(Synopsys, Inc., 纳斯达克股票代码:SNPS)近日宣布,其行业领先的IC Compiler™ II布局布线解决方案成

关键字:

新思科技 IC Compiler II Graphcore

重点:3DIC Compiler基于新思科技的Fusion Design Platform、世界级引擎和数据模型,在单一用户环境下提供一个综合性的端到端解决方案,具有针对先进多裸晶芯片系统设计的全套功能提供强大的三维视图功能,为2.5D/3D封装可视化提供直观的环境,显著减少设计到分析的迭代次数,并最大限度地缩短整体集成时间提供与Ansys硅-封装-印刷电路板技术的紧密集成,以进行系统级信号、功率和热量分析新思科技(Synopsys, Inc.,纳斯达克股票代码:SNPS)近日推出其3DIC

Co

关键字:

新思科技 3DIC Compiler

重点:IC Compiler II和Fusion Compiler的机器学习技术助力三星将频率提高高达5%,功耗降低5%机器学习预测性技术可加快周转时间(TAT),使三星能够跟上具挑战性的设计时间表三星在即将推出的新一代移动芯片流片中部署了机器学习技术新思科技(Synopsys,

Inc.,纳斯达克股票代码:SNPS)今天宣布,三星(Samsung)为其新一代5纳米移动芯片生产设计,采用了IC Compiler™

II布局布线解决方案(新思科技Fusion Design

Platform™的一

关键字:

三星 新思科技 IC Compiler II 机器学习 5纳米 SoC

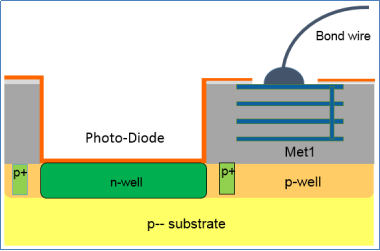

引言 更小的外形尺寸、卓越的功能、更出色的性能和更低的BOM(物料成本)是系统工程师在开发传感器和传感器接口应用等复杂电子产品时面临的主要挑战。缩小芯片尺寸可以通过使用集成密度更高的小型制程节点实现,而系统的小型化则可以通过使用先进的封装技术来达成。如今,对更高系统集成度的需求与日俱增,这也促使那些传统的封装服务供应商和半导体公司着手开发更具创新性、更为先进的封装技术。其中前景广阔,同时也具有挑战性的当属采用硅通孔(TSV)的3D集成电路(3DIC)。3DIC技术现已被广泛应用于数字集成电路(例如存

关键字:

3DIC 传感器

半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司(Nasdaq:SNPS)日前宣布:该公司在其Galaxytrade;设计实现平台中推出了最新的创新RTL综合工具Design Compilerreg; 2010,它将综合和物理层实

关键字:

Compiler Design 布局

新思科技(Synopsys, Inc.)日前发布全新定制设计解决方案Custom Compiler™。Custom Compiler™将定制设计任务时间由数天缩短至数小时,消弭了FinFET的生产力差距。为了将FinFET版图生产力提升到新的高度,Synopsys采用了新颖的定制设计方法,即开发视觉辅助自动化技术,从而提高普通设计任务的速度,降低迭代次数并支持复用。通过与行业领先的客户的密切合作,Custom Compiler已经在最先进的节点上进行生产工作,并

关键字:

新思 Custom Compiler

国内年度半导体业展会盛事「SEMICONTaiwan2014」九月三日至五日举行。主办单位「国际半导体设备材料协会」(SEMI)台湾区副总裁何玫玲表示,此次展览规模,创下历年最高纪录,总计超过六百五十家厂商、一千四百一十个摊位,参展厂商和参观人数则突破四万。比起去年,何玫玲直言,今年展览买气强旺,买主洽谈会共约六十场,这是往年没有发生的现象。

2014年半导体展概念股台厂营运情形

何玫玲分析并解释说,买气旺盛,应是国内龙头厂商台积电(2330)、联电(2303)等,近年大力扶持国内

关键字:

半导体 晶圆代工 SEMICONTaiwan2014 3DIC 2.5DIC

3D IC将是半导体业者站稳手机晶片市场的必备武器。平价高规智慧型手机兴起,已加速驱动内部晶片整合与制程演进;然而,20奈米以下先进制程研发成本极高,但所带来的尺寸与功耗缩减效益却相对有限,因此半导体厂已同步展开3D IC技术研发,以实现更高的晶片整合度,其中,三星已率先宣布将于2014年导入量产。

拓墣产业研究所半导体中心研究员蔡宗廷认为,MEMS技术将是手机设计差异化的关键,包括MEMS自动对焦和振荡器的出货成长均极具潜力。

拓墣产业研究所半导体中心研究员蔡宗廷表示,2013~2015

关键字:

手机芯片 3DIC

在西安市高新开发区管委会大力支持下,SEMI中国封测委员会第五次会议近日在西安成功召开。SEMI全球副总裁、中国区总裁陆郝安与西安高新开发区安主任共同为会议致辞,吴凯代表SEMI中国同与会者分享了中国半导体及封测市场现况、SEMI标准制定流程和重要意义、SEMI标准在北美的成功案例等主题报告。经过热烈讨论,代表们就3DIC标准的制订在以下几个方面达成共识:

一是台湾和北美对3DIC发展方向也不明确,中国半导体投资巨大且贴近应用市场,有机会赶上欧美先进水平,甚至在特定领域可实现"弯道

关键字:

封测 3DIC

中芯国际集成电路制造有限公司(中芯国际)宣布成立视觉、传感器和3DIC中心(简称CVS3D)。中芯国际CVS3D整合、强化了中芯国际在硅传感器、通过硅通孔(TSV)技术和其他中端晶圆制程技术(MEWP)的上的研发和生产制造能力。而MEWP技术带动了在CMOS图像传感器、MEMS传感器、三维堆叠设备,和基于TSV2.5D和3D的高性能系统级封装(SiP)方面的显著进步。

半导体行业正快速采用基于TSV2.5D和3DIC的技术,使系统芯片进一步小型化,同时降低功耗、提高设备和系统性能。根据201

关键字:

中芯国际 3DIC

过去一年中,Mentor公司实现了10亿美元的营业额。并在20nm设计、3DIC、DFM(可制造设计)、DFT(可测试设计)、SoC验证方面都有很大进展。在北京的Mentor Forum期间,笔者就目前设计业的一些困惑,询问了Mentor的掌舵人。

关键字:

Mentor 3DIC

半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司(Nasdaq:SNPS)日前宣布:该公司在其Galaxytrade;设计实现平台中推出了最新的创新RTL综合工具Design Compilerreg; 2010,它将综合和物理层实

关键字:

Compiler Design 2010 布局

3dic compiler介绍

您好,目前还没有人创建词条3dic compiler!

欢迎您创建该词条,阐述对3dic compiler的理解,并与今后在此搜索3dic compiler的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473